模式

AG32芯片内的两个核和两个bin

一、概述

与传统单核芯片(如:ST系列)不同,AG32整颗芯片包含两个核:MCU和CPLD。

- MCU核:已经相当于ST的整颗芯片。

- CPLD核:是比普通芯片多出来的那个核。

这两个核是相互独立的(各自编译、各自下载),又可以相互连通起来(信号连通)共同工作。

因此,AG32工程会编译出2个bin:

- code.bin:MCU部分的代码。

- logic.bin:CPLD部分的逻辑。

最终使用时,需要把这两部分的bin都烧录进去,芯片才能工作起来。

- MCU的bin:在VScode下点编译即可生成。

- CPLD的bin:根据使用方式的不同,生成方式也会不同。

二、两个bin怎么生成

根据使用预期的不同,分成三种情况:

- 只使用MCU部分,不使用CPLD部分

- 同时使用MCU和CPLD来联合编程

- 只使用CPLD部分,不使用MCU部分

以上3种方式都会生成2个bin。只不过情况1和情况3生成出来的第二个bin是系统自动生成的,用户无感。

情况1:只使用MCU部分

- 配置:VE文件里只配置MCU用到的PIN脚。

- 生成bin:在VScode工程中点“Upload LOGIC”时,会自动生成默认的logic.bin(用户逻辑为空),并编译出bin,再烧录,一键完成全过程。

- 开发者体验:logic部分对开发者无感。

情况2:同时使用MCU和CPLD

- 配置:VE文件里需要配置MCU和PIN之间、MCU和CPLD之间、CPLD和PIN之间的信号关联。

- 生成bin:

- 在VScode下点“Prepare LOGIC”按钮,生成CPLD的空的框架工程。

- 开发者在该框架下完成CPLD逻辑的编写和调试。

- 编译生成cpld.bin。

- 烧录:在VScode下点“Upload LOGIC”烧录。

情况3:只使用CPLD部分

- 开发环境:在Quartus环境下完成CPLD开发。

- 生成bin:

- 首先生成cpld.bin并调试。

- MCU的bin由系统自动生成。

- 开发者体验:与情况1相反,CPLD.bin由开发者调试生成,MCU.bin由系统自动生成。

三、两个bin怎么调试和烧录

- MCU调试:在VScode下进行。

- CPLD调试:使用Quartus和Supra工具,支持模块级测试(如Modelsim)。

- 烧录:

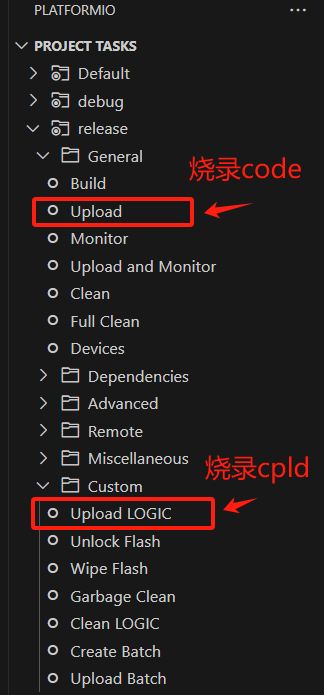

- VScode下使用“Upload”和“Upload LOGIC”按钮分别烧录code.bin和logic.bin。

- Supra下使用Upload功能烧录CPLD。

- 生产烧录:生成二合一的batch.bin,使用downloader.exe工具烧录。

四、Flash大小与两个bin的烧录位置

Flash大小

AG32系列中,Flash大小有两个型号:256K和1M。

- 起始地址:0x80000000。

- 可擦写块大小:4K(每次擦写的最小单位为4K,起始地址需4K对齐)。

bin的存储位置

- code.bin:默认存储在0x80000000。

- logic.bin:默认存储在最后100K。

无论Flash是256K还是1M,最后100K都留给CPLD使用。

- 256K Flash:156K程序 + 100K CPLD.bin。

- 用户程序不能超过156K,否则会冲掉logic部分,导致程序运行异常(如系统时钟初始化失败)。

- 调整存储界限:

board_logic.compress = true:对CPLD.bin进行压缩,通常小于48K。board_upload.logic_address = 0x80034000:调整CPLD.bin的起始点。

bin的运行

- code.bin:在Flash区域运行。

- logic.bin:被加载到CPLD内核区域运行(非128K RAM区)。

五、其他说明

在使用MCU时,如果不用CPLD部分,CPLD是否多余?

不是的。

整个芯片的开发依赖于配置文件.ve。在该文件中,需要配置使用的时钟和全部引脚。这些配置会生成到CPLD.bin中。

- MCU信号和引脚:需要CPLD的参与,MCU的信号才能最终使能到引脚。

- 详情:请参考引脚配置。